**MSMF GATE CENTRE**

**SUB: DIGITAL ELECTRONICS**

| 1. | For the circuit shown in figure, the output F will be |             |                      |                |               |                    |                |                      |  |

|----|-------------------------------------------------------|-------------|----------------------|----------------|---------------|--------------------|----------------|----------------------|--|

|    | •                                                     | XOR         | XOR                  | XOR            | F             |                    |                |                      |  |

|    | (a) 1                                                 | •<br>(b) z  | •<br>ero             | (c) X          |               | (d) $\overline{X}$ |                |                      |  |

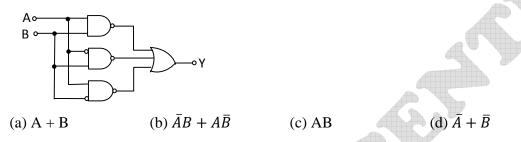

| 2. | The Bool                                              | lean expres | ssion for the o      | output Y in    | the logi      | c circuit is       |                |                      |  |

|    |                                                       |             | А                    |                |               |                    |                |                      |  |

| A  |                                                       | A           | B<br>C               |                | Y             |                    |                |                      |  |

|    | (a) $A\overline{B}C$                                  |             | (b) ABC              |                | (c) <i>ĀB</i> | c 🚺                | (d) <i>ĀĒĒ</i> |                      |  |

| 3. | The outp                                              | ut X of the | circuit show         | n in the fig   | ure will      | be                 |                |                      |  |

|    | (a) AB                                                |             | (b) <i>ĀB</i>        |                |               | -                  |                |                      |  |

|    | (c) $A\overline{B}$                                   |             | (d) $\bar{A}\bar{B}$ |                |               |                    |                |                      |  |

| 4. | For logic                                             | circuit sho | own, the requ        | ired inputs    | A,B and       | l C to make t      | the output X = | 1 are, respectively, |  |

|    | (a) 1,0 ar                                            |             | (b) 0,0 and 1        |                |               | A f<br>B           |                |                      |  |

|    | (c) 1,1 an                                            | nd 1        | (d) 0,1 and 1        |                |               | С                  |                | х                    |  |

| 5. | The circu                                             | iit shown b | elow generat         | tes the func   | tion of       |                    |                |                      |  |

| Z  | x ·<br>y ··                                           |             |                      |                | f             |                    |                |                      |  |

|    | (a) x ⊕ y                                             | ,           | (b) 0                | (c) x <i>y</i> | + yx + j      | ÿx (d) x           | к. <u></u> у   |                      |  |

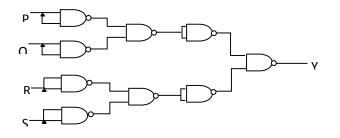

6. For the circuit shown in the figure the Boolean expression for the output Y in terms of inputs P, Q, R and S is

(a)  $\bar{P} + \bar{Q} + \bar{R} + \bar{S}$  (b) P + Q + R + S (c)  $(\bar{P} + \bar{Q})(\bar{R} + \bar{S})$

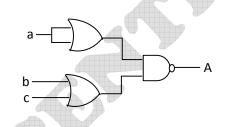

- 7. The output a of the circuit shown below is

- (a)  $\bar{a} + \bar{b}\bar{c}$  (b) a + bc(c)  $\bar{a}\bar{b} + \bar{a}\bar{c}$  (d)  $a + b\bar{c}$

(d) (P + Q) (R + S)

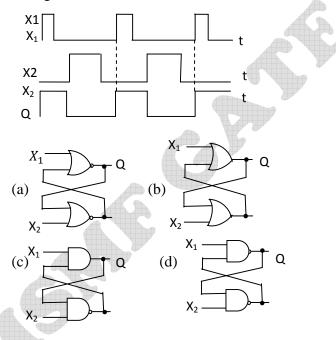

8. Select the circuit which will produce the given output Q for the input signals  $X_1$  and  $X_2$  given in the figure

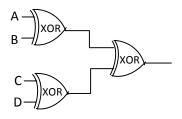

**9.** A, B, C, and D are input, and Y is the output bit in the XOR gate circuit of the figure. Which of the following statements about the sum S of A, B, C, D and Y is correct?

(a) S is always with zero or odd

- (b) S is always either zero or even

- (c) S = 1 only if the sum of A, B, C and D is even

- (d) S = 1 only if the sum of A, B, C and D is odd

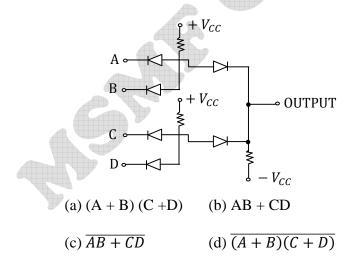

**10.** In the given circuit, the output Y equals which one of the following?

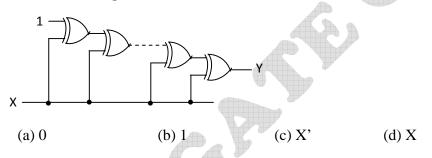

**11.** If the input to the digital circuit of the figure consisting of cascade of 20 XOR gates is X, then what is the output Y?

12. What is the output of the gate circuit shown in the figure?

- **13.** A digital circuit which compares two numbers  $A_3A_2A_1A0$ ,  $B_3B_2B_1B_0$  is shown in figure. To get output Y = 0, choose one pair of correct input numbers.

- (a) 1010, 1010 (b) 0101, 0101 (c) 0010, 0010 (d) 1010, 1011 14. The circuit shown is functionally equivalent to which one of the following? А В f А В (a) NOR gate (b) OR gate (c) EX-OR gate (d) NAND gate 15. The Boolean expression for the shaded area in the Venn diagram shown is (a) A +  $\overline{B}$  + C (b)  $AB + \overline{ABC}$ (c)  $A\overline{B}C + \overline{A}BC$  (d)  $AB + \overline{A}\overline{B}C$ 16. The Boolean expression Y(A, B, C) = A + BC is to be realized using 2-input gates of only one type. What is the minimum number of gates required for the realization? (a) 1 (b) 2 (c) 3 (d) 4 or more 17.

- The Boolean expression  $X(P, Q, R) = \pi(0,5)$  is to be realized using only two 2-input gates. Which are these gates?

- (a) AND and OR (b) NAND and OR (c) AND and XOR (d) OR and XOR

- **18.** Assume that only x and y logic inputs are available, and their complements  $\bar{x}$  and  $\bar{y}$  are not available. What is the minimum number of 2-input NAND gates required to implement  $x \oplus y$ ? (a) 2 (b) 3 (c) 4 (d) 5

- 19.The NAND-NAND realization is equivalent to<br/>(a) AND-NOT realization(b) AND-OR realization(c) OR-AND realization(d) NOT-OR realization

- 20. Which one of the following statements is correct? For a 4-input NOR gate, when only two inputs are to be used, the best option for the used inputs is to (a) connect them to ground (b) connect them to  $V_{cc}$ (c) keep them open (d) connect them to the used inputs

- 21. Minimum number of two input NAND gates required to realize the logic function  $(A\overline{B} + \overline{A}B)$  is (a) 5 (b) 3 (c) 6 (d) 4

- **22.** According to De-Morgan's second theorem

- (a) A NAND gate is always complementary to an AND gate

- (b) An AND gate is equivalent to a bubbled NAND gate

- (c) A NAND gate is equivalent to a bubbled AND gate

- (d) A NAND gate is equivalent to a bubbled OR gate

- **23.** If  $\bar{x} + \bar{y} = 0$ , then which one of the following is true?

(a)  $\overline{x}y + \overline{y}x + xz = x\overline{y} + yz$ (b)  $\overline{x} \overline{y} \overline{z} + xyz = xy\overline{z} + \overline{x} \overline{y} \overline{z}$ (c)  $\overline{x}y + \overline{y}x + = xy + \overline{x}\overline{y}$ (d)  $\overline{x}yx = 1$

- 24. The POS form of expression is suitable for circuit using (a) XOR (b) NAND (c) AND (d) NOR

- **25.** Sum of product representation of Boolean equations can be easily realized by the following digital circuits

(a) NAND-NAND (b) AND-AND (c) OR-OR (d) NOR-NOR

## KEY FOR DIGITAL ELECTRONICS

| 1-B          | 2-B  | 3-B  | 4-C  | 5-A  | 6-B  | 7-A  | 8-A  | 9-D  | 10-D |

|--------------|------|------|------|------|------|------|------|------|------|

| 11-B<br>21-B | 12-B | 13-D | 14-C | 15-D | 16-C | 17-D | 18-C | 19-B | 20-D |

| 21-B         | 22-D | 23-A | 24-D | 25-A |      |      |      |      |      |

|              |      |      | 6    |      |      |      |      |      |      |